Inter-Integrated Circuit:-

The I2C protocol is a half-duplex synchronous two wired multi-master serial communication protocol invented by Philips Semiconductor in 1989.

We discuss each word in the above sentence.

Half Duplex:- It says that the data flow is either form Master to slave or from Slave to Master not in both directions simultaneously.

Synchronous:- It means the sender always gets the acknowledgment response from the receiver after successful data received.

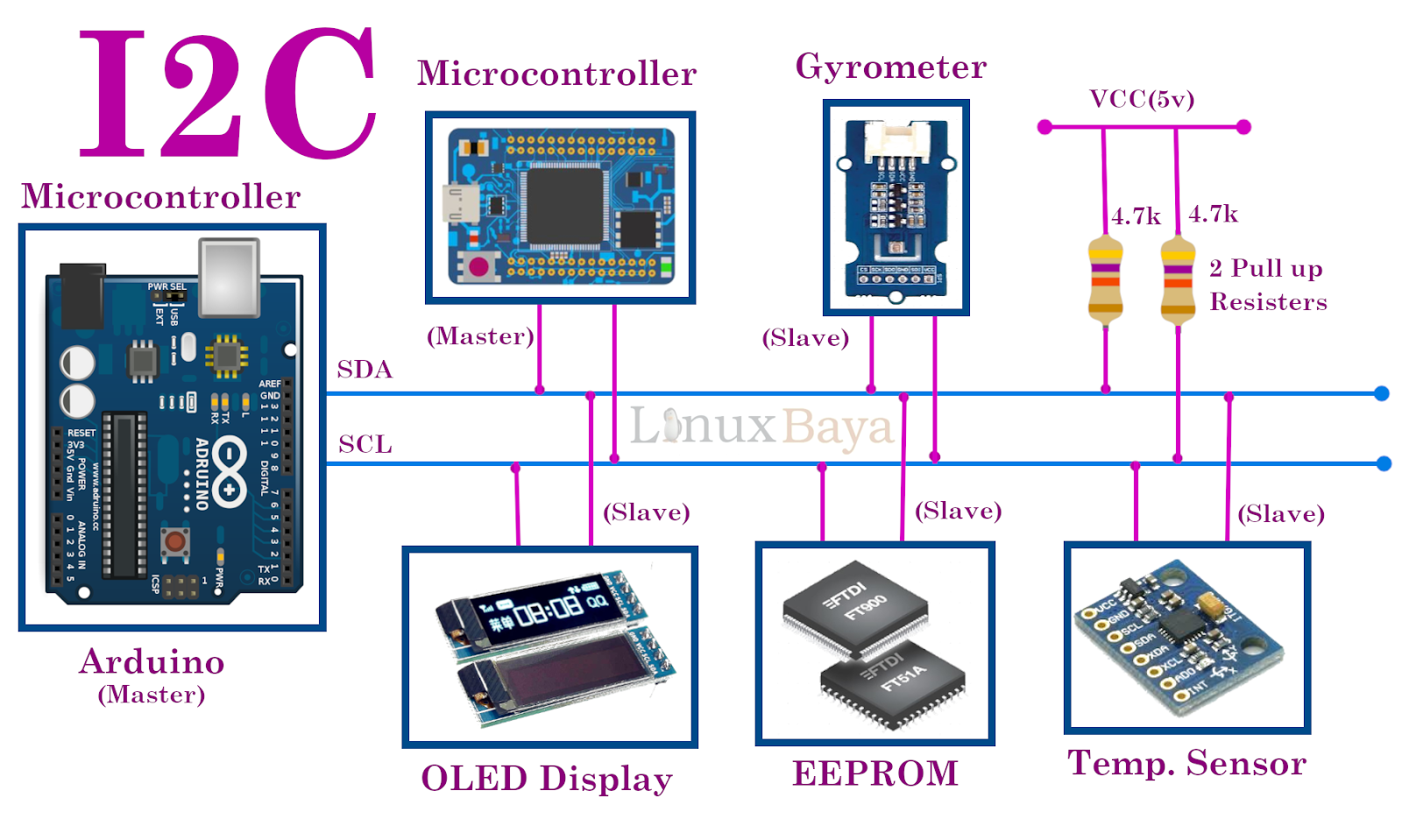

Two wired:- To successful transfer data it required only two wires (SDA and SCL).

SDA:- To transfer data bit.

SCL:- To transfer clock bit (SCL gives the synchronous to I2C)

Multi-Master:- It means multiple devices can be connected on a single bus. You can see the above figure where two Microcontrollers are connected to a single bus. They can communicate with any slave.

Serial Communication:- It means the data transfer from the sender to the receiver is bit by bit up to one byte.

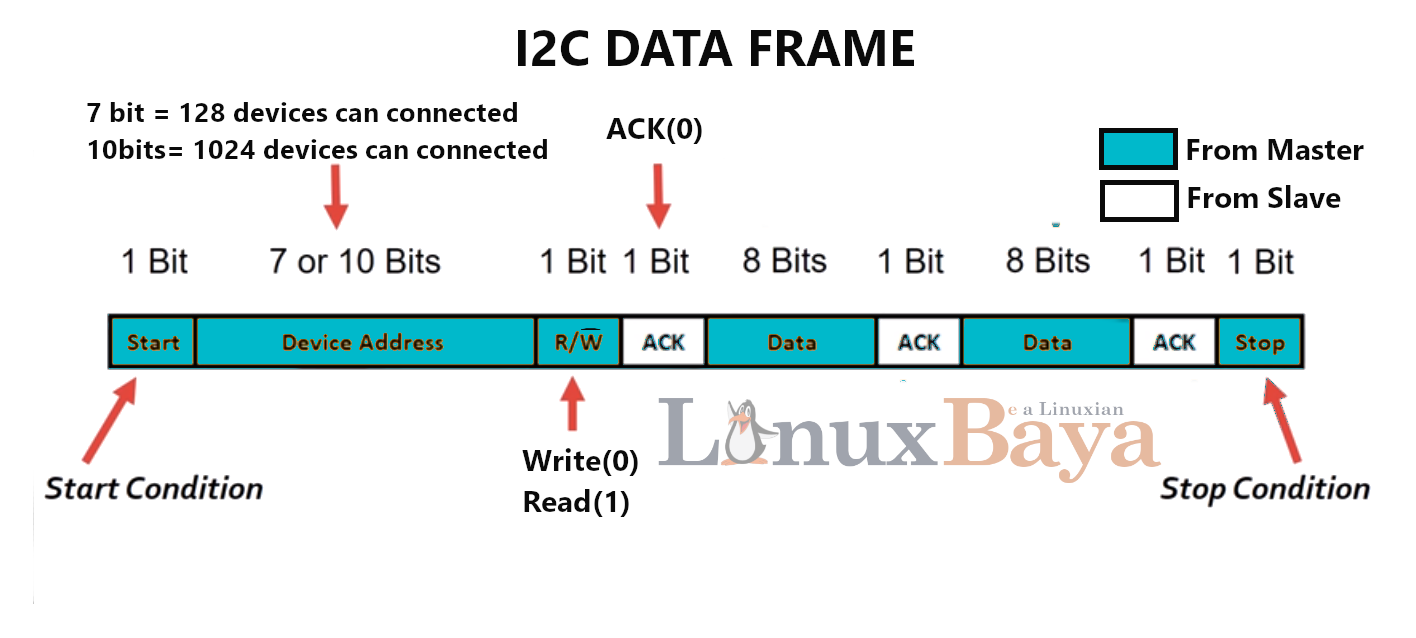

Before the master sending the actual data to the slave master needs to configure the BUS by sending the start bit, Address of slave and Read/Write bit, Then master gets an ACK bit from the slave, After that, the master starts sending the data and after successful sent it receives an ACK bit and then sends another packet of data. When it successfully sends all data master terminates the communication by sending the stop bit.

Start, Stop bits are the conditions of the flow of 1 and 0 in SDA and SLC line.

START occurs when the SCL is 1 and SDA goes 0 to 1.

END occurs when the SCL is 1 and SDA goes 1 to 0.

ACK occurs when the SDA is 1 and SCL goes 0 to 1.

(Ack bit always flows opposite towards the data bit.)

|

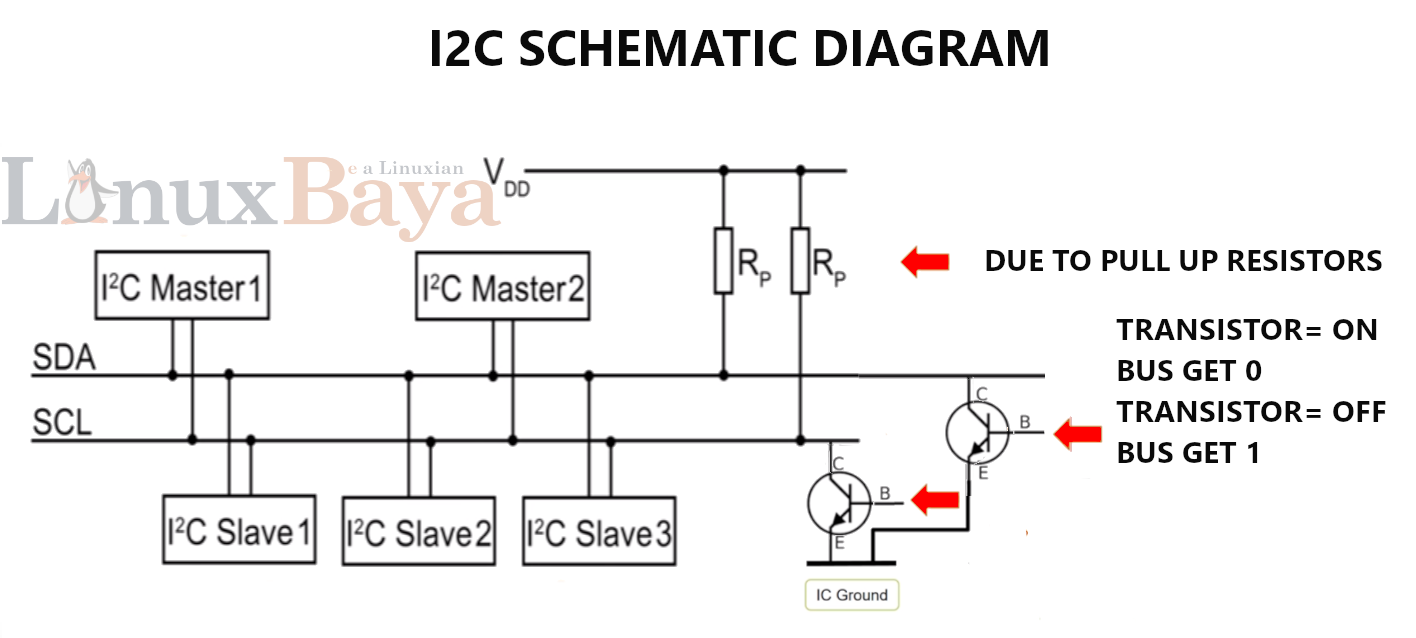

| The diagram shows how the bus achieves 0 or 1. |

There are two pull up resistors and two open collector BJT transistors are connected to two bus lines. Let's consider the transistors are switches when the transistor goes OFF the current flow from the Vdd makes the bus active. when the transistor goes ON transistor grounded the Vdd current and makes inactive to the BUS.

How Multi-master works on a single bus at the same time?

Arbitration:- By constantly monitoring the bus a master can determine the bus condition either it is ideal or busy. If busy it delays its transfer until the stop bit. If multiple masters start transferring the data at the same time, whoever sends zero first that wins. This is called Arbitration.

In the above figure, 3 Masters are try to send the slave address through the bus simultaneously. So All 3 masters send the first MSB. Although all having their MSB 1, so no one can lose its arbitration. When any master sends the 0 bit first then it wins the arbitration and able to send its slave address through the bus.

Clock Stretching:- Slave device may hold the clock line low after receiving a byte. Which indicates slave is not ready to receive data. So the master waits until the clock goes high.

Advantage:- Due to device addressing no chip select pin is required. Better error handling with ACK bit.

Disadvantage:- Slow-speed because of the frame overhead due to device address bit and ACK bit. Speed is up to 3.4MHz clock(high-speed mode).

Similar Topics:-