There are seven interrupts in ARM 7. Interrupts are nothing but a system exception that makes the processor enter into different modes. There are seven operating modes in ARM 7 also. Please don't think seven interrupt makes the processor switch to seven modes. There are two modes, user and system modes don't require any interrupt to acquire its mode.

Once the processor will start it comes to the supervisor mode after the OS loaded it automatically goes to the user mode, no interrupt is occurring this. From the user mode, we invoke the system function and goes to system mode and do the job and get back to user mode and again no interrupt will need.

The seven interrupts are called:-

- Reset

- Undefined Instruction

- Software Interrupt

- Prefetch Abort

- Data Abort

- IRQ (Normal Interrupt)

- FIQ (Fast Interrupt)

Reset:-

Some processor reset is not called an interrupt but In ARM processor the reset is called an interrupt. No need to explain what it does. When we press the reset button it restarts the machine. When the processor restarts it directly not goes to user mode, first it loads the OS set the things for you up to 20-30 sec and then gives the user mode. So the reset interrupt goes to the supervisor mode.

Undefined:-

This interrupt called when the processor can't decode the fetched instruction. That means While we doing the operation the processor fetches the instruction and then decodes the fetched instruction to do execution. Instructions are stored in the form of upcodes. if the specific upcode is to present in the main ARM processor then it can't find what to do with that instruction so it goes to the undefined state and kill the operation and come back to user mode.

SWI:-

This interrupt will occur when the user wants to do some serious job with the help of its Operating System. for ex:- On our phone if we want to delete some things. or wants to install some things. we just choose the option to delete or install. but inside this, the control goes to the supervisor mode from user mode and executes the operation of deleting or installing then comes back to the user mode. This SWI and Reset interrupt both goes to the supervisor mode.

But the reason is totally different. In reset, it goes to supervisor mode to boot the OS but in SWI it goes for doing the user action from user mode and comes back to the user mode.

Prefetch & Data Abort:-

We know that in a processor we have different privileges for protection. So we have system privilege and user privilege. system privilege contains a system program and system data. user privilege contains user programs and user data.

the system has access to manipulate data and programs in user privilege but the user can't access the system privileged data and program.

So when the user wants to access the system program that means you are fetching instruction that doesn't have the permission to access then it goes to prefetch abort mode.

And when it tries to access the system data without permission then it goes to the data abort mode.

IRQ and FRQ:-

These are two external hardware interrupts. ARM contains two external PIN for IRQ and FIQ. If it got an interrupt on IRQ, it go to IRQ mode. If it got an interrupt on FIQ it goes to FIQ mode.

IRQ is executed at the normal based. and FIQ is executed in faster based.

All interrupts has its own address called vectors.

You might notice one thing on the above figure, all interrupt vector having the same byte of memory distance between them i.e 4byte.

Because as we know we the interrupt occur processor goes to ISR and executes the defined operation by the programmer and comes back. So the programmer can define an ISR(Interrupt function) of variable size that can't be predicted. So what we need to do? When the interrupt occurs we just need to pass the ISR(function) address and make a jump to ISR address. So to make jump or branch to ISR location it needs just one instruction. So ARM having the instruction of the same size i.e 32bit or 4byte. This jump or branch instruction is also needed for 4byte memory. That's why there is a gap of 4byte In each interrupt's address.

And also you might notice there are two addresses called lower vector and higher vector. one thing we must need to remember is all the interrupts have to be in program memory i.e RAM. So the total memory starts from 00000000 to FFFFFFFF in between these the RAM and ROM are allocated. If RAM is present with starting address FFFFFFFF and ROM is present with starting address 00000000 then you must use the lower vectors for interrupts. And if the ROM is present with starting address FFFFFFFF and RAM with starting 00000000 then we must need to use the higher vectors for the interrupts.

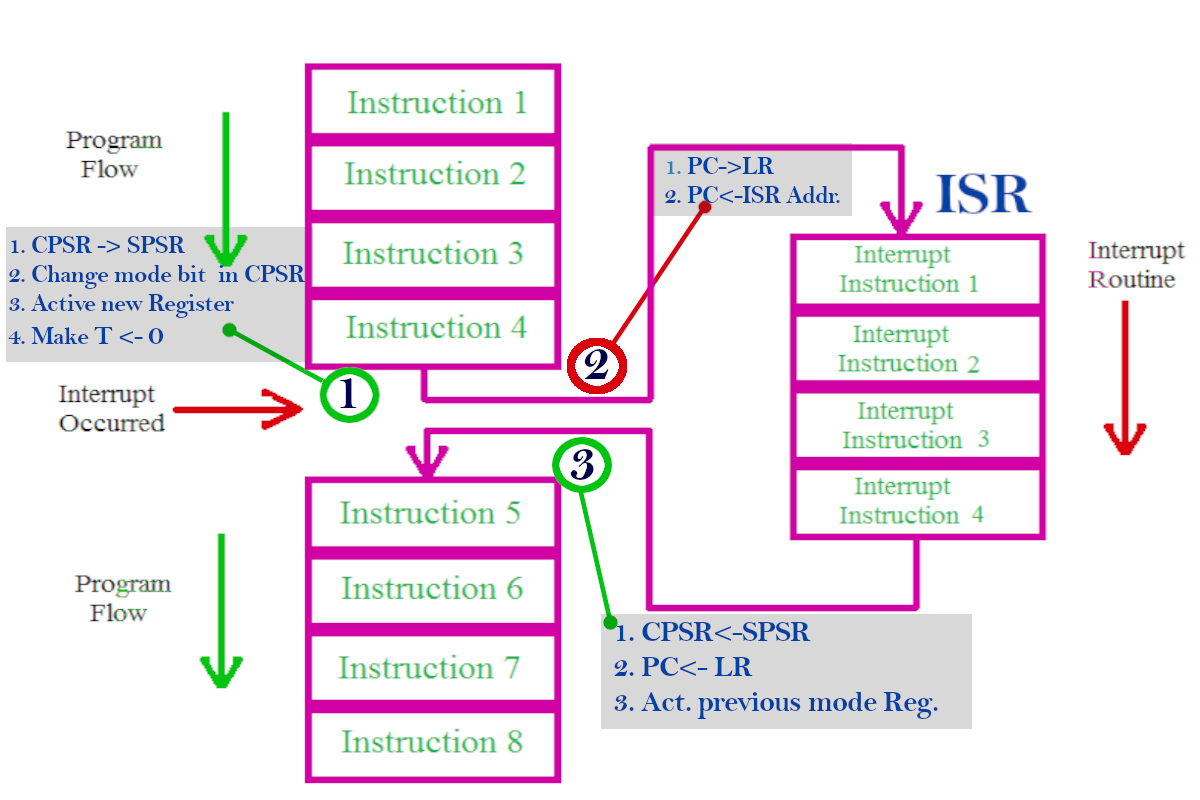

The procedure followed when an interrupt occurs.

1. First, save the CPSR value to SPSR.

2. Change the mode bit in CPSR.

3. Activate the new Registers according to the Mode Of operation.

4. Make T bit to 0(T=0). Because the main program can have two states, a normal state or thumb state. But the ISR can't be in two states, it always in a normal state.

5. Load the Program counter (PC) value to LR.

6. Load the ISR address to PC.

7. Then the ISR execution starts.

8. After finish the ISR execution Load the SPSR value s to CPSR.

9. And LR value to PC.

10. Reactivate the previous mode registers.

When you go to any ISR the "i" bit in CPSR is disable. which means the IRQ is disabled. And the two Interrupts Reset and FIQ make the FIQ bit disable. Because when we are in reset Interrupt system is in BIOS mode so here FIQ can't interrupt the mode so it is disabled. and in FIQ ISR it's already in FIQ mode so the FIQ bit of CPSR is disabled.

Also, Read👇

Also, Read👇